In late 2021 I wrote this brief article around skills a network engineer should pick on in his/her early career. Where I suggested to be at least familiar with basic understanding of both "Router Architecture" & "ASIC Architecture". Now obviously the depth is always subjective to:

1. How many details I need to know for my current role & responsibilities in order to get things right

2. The amount of details and depth I need to know for potential future roles that you might be targeting

3. Your personal curiosity & interest

4. If you are really into Architecture & Design, You got to have fair & intermediate level of understanding of these topics at minimal

5. If you into Pre-sales, You often got to deal with sizing & performance for a given set of equipment as part of your deliverables requested by client in the form of RFP or RFI. Remember those data sheets you often have to refer to claiming IPv4 or IPv6 prefixes numbers a platform can hold/support ?

6. You might have to do platform testing at some point as part time or full time job including you may land yourself into a COE (Centre of Excellence) of your organization or may end up into a "Platform/Service Product Management" role.

Now you must know that often those specifics and details are hidden and never publicly shared/offered by most of ASIC/Platform vendors. You often got to be a premium customer and sign-off tons of NDAs to get those details to some extent and more importantly you got to be very specific around what exactly you are looking for since asking for data in abstraction would often result into tons of non-specific information thrown on you by your fav. ASIC vendor.

Assuming by now you have some more clarity in terms of why you need to know all these details as a Network engineer depending upon where you are and where you plan to end up, lets circle back to original topic for today which is "How many IPv4 (could be IPv6) prefix my device support in reality?"

Which leads us to a simple question - "What are the different variables I am dealing with when trying to figure how much routes my platform can really hold?"

While a simple answer you would often hear would be "it depends" or someone may point your to RFC-1925 rule 8 "It is more complicated than you think"

So let's try to list some of them in this series Part - 1

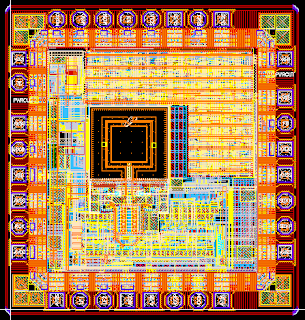

- ASIC Architecture

- ASIC pipeline

- Memory architecture

- Memory Carving/allocation to different features & functions (HW/SW)

- How the information is queued & de-queued

- API details (Type of API, API interface, Information flow etc.)

- Routing Vs. Switching ASIC

- Hierarchical vs. A Flat FIB

- NOS Architecture

- How NOS is programming the FIB

- Prefix Length

- Contiguous Vs. Dis-contiguous Prefixes

- Sorting Algorithm & Data Structures

- Device Profiles/Resource Allocations by NOS

- NOS Scheduler

- ECMP, UCMP, FRR

- Platform Architecture

- Line Card Architecture

- Back Plane Architecture

Further Readings:

ASIC

ASICs for Network Engineers

A Brief History of Router Architecture

Anatomy of Core Network Elements

SONiC: Open Source NOS in Data Cente

Cisco - Configuring SDM Resource Allocation Templates

Adjacency Matrix, Adjacency List, Priority Queue Implementation

Juniper Networks Routing ASIC Strategy

Cisco 8000 Series - Under the Hood

Sizing Router Buffers - Small is the New Big...

Embedded Hardware for Processing AI at the Edge: GPU, VPU, FPGA, and ASIC Explained

ASICs vs. Net Processors: Understanding the True Costs

P4 - Programming Protocol-Independent

Open Flow Specifications - Remember how Open Flow Originally planned to program the ASIC directly using Open Flow Controller ?

How Routers Really Work - A Webinar from Russ White under O'Reilly Subscription

Networking Hardware/Software Disaggregation in 2022

Select the Best Switching ASIC For the Job

Data Center Switching ASICs Tradeoffs

Switching Hardware Series - Part 1 , Part 2 & Part 3

Juniper MX10000 LC480 Deepdive

Using Trio -- Juniper Networks' Programmable Chipset -- for Emerging In-Network

Optimizing Power Consumption in High-End Routers

Striking a Balance: Exploring Fairness in Buffer Allocation and Packet Scheduling

Making 35 000 000 IP lookup operations per second with Patricia tree

Optimizing Power Consumption in High-End Routers

Saving Energy on PTX with PFE Power Off

ACX7000 L2 MAC Scale and Learning Rate

FIB Compression in Juniper Routers

PTX10001-36MR FIB Install Rate

Express 4 Filters - Foundation

Large Language Models — the hardware connection

Classification TCAM with Cisco CloudScale ASICs for Nexus 9000 Series Switches White Paper

Chiplets - The Inevitable Transition

[Podcast] The chips are down: Moore’s Law coming to an end

HTH...

A Network Artist 🎨